Bonjour,

J'ai configuré la signalisation de mon réseau avec l'outil SSL (Logique du Signal Simple) de JMRI.

Cet outil pilote les signaux individuels simples (Vert-Jaune-Rouge) type bloc automatique lumineux (BAL).

On définit ainsi simplement en quelques clics toute la signalisation de son réseau.

https://www.jmri.org/help/fr/html/tools/signaling/SimpleSignalExample.shtmlJ'ai 52 signaux (4 signaux par aiguillages plus 4 signaux de cantons pleine voie).

Ces signaux figurent sur l'écran de mon TCO de PanelPro et ils sont mis à jour en temps réel.

Layout3.jpg

J'ai souhaité installer sur mon réseau une douzaine de sémaphores 3 feux correspondant à ces signaux aux endroits les plus stratégiques.

J'ai réalisé une modélisation CAO 3D de ce sémaphore et j'ai exporté les fichiers 2D pour une fabrication par photogravure.

semaphore_CAO.jpg

J'ai sous traité la fabrication d'une plaque en laiton 0.2 mm au format A4 permettant la fabrication de 14 sémaphores.

Je me suis adressé à la société Hauler (République Tchèque) qui a réalisé un travail parfait pour 34€ port compris.

https://www.hauler.czplaque laiton.jpg

semaphores peints.jpg

J'ai soudé sur chaque sémaphore 3 diodes leds CMS Vert-Jaune-Rouge cathode à la masse et anode soudée à un fil émaillé 0.3 mm.

La commande de la tige du sémaphore s'effectue avec un mini sevo moteur SG90 placé sur un support imprimé 3D sous la voie.

L'idée étant que le sémaphore soit à l'équerre lorsque le feu est rouge (signal stop) et qu'il soit relevé pour un feu jaune ou vert.

Pour commander ces signaux j'utilise ma carte (24 entrées) 48 sorties (arduino-CMRI) reliée à JMRI.

https://forum.locoduino.org/index.php?topic=507.0J'utilise 36 sorties (3 x 12) affectées à chaque feu des signaux définis dans JMRI.

carte CMRI.jpg

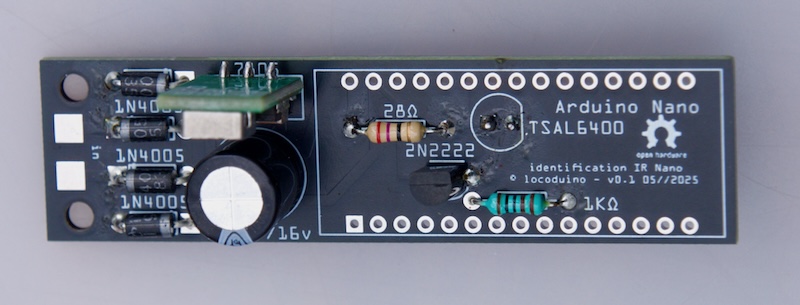

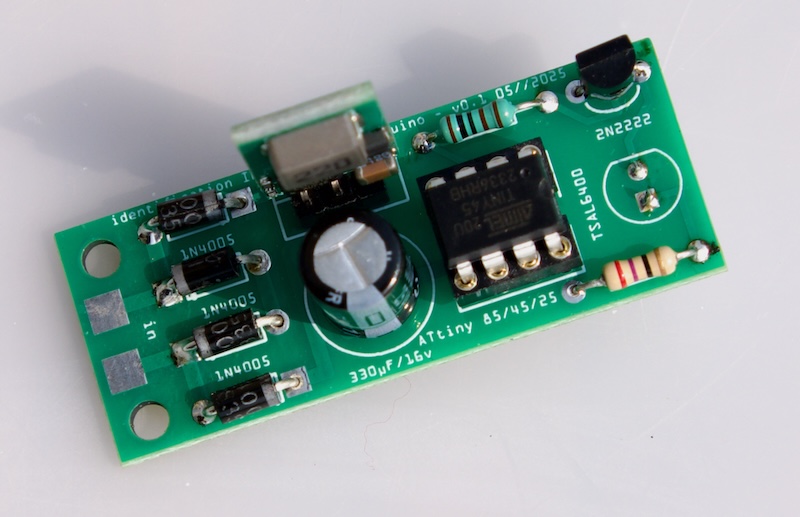

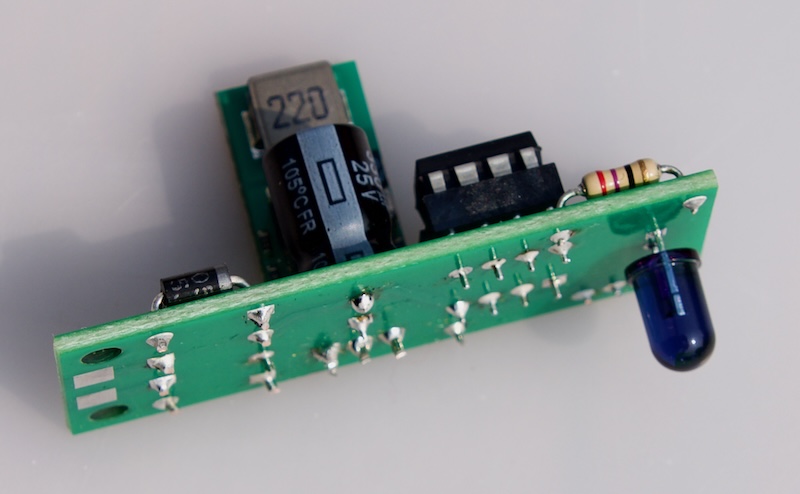

Pour commander chaque servo de sémaphore j'ai réalisé un petit circuit à base d'ATtiny13A.

L'ATtiny13 est un mini microcontroleur (1 K Flash) 8 pins. Compatible Arduino. L' ATtiny13A est la version "Low Power".

Son prix est particulièrement bas, environ 0,40€ pièce (par 10 en CMS SOP8) sur AliExpress.

https://fr.aliexpress.com/item/1005007265849889.html?srcSns=sns_Gmail&spreadType=socialShare&bizType=ProductDetail&social_params=61115567768&aff_fcid=78fc8967806f407f8d17475718e00806-1748010217919-05569-_EQLLbjY&tt=MG&aff_fsk=_EQLLbjY&aff_platform=default&sk=_EQLLbjY&aff_trace_key=78fc8967806f407f8d17475718e00806-1748010217919-05569-_EQLLbjY&shareId=61115567768&businessType=ProductDetail&platform=AE&terminal_id=2ccab959b9674ce68c71c9f0693923f9&afSmartRedirect=yJ'ai soudé chaque ATtiny13A CMS sur un mini circuit imprimé adaptateur SOP8 vers DIP8.

https://fr.aliexpress.com/item/1005008144822733.html?srcSns=sns_Gmail&spreadType=socialShare&bizType=ProductDetail&social_params=61115562188&aff_fcid=9e1f43dc518c4636ab8d9d925431292d-1748009948365-07178-_EQ8B9D8&tt=MG&aff_fsk=_EQ8B9D8&aff_platform=default&sk=_EQ8B9D8&aff_trace_key=9e1f43dc518c4636ab8d9d925431292d-1748009948365-07178-_EQ8B9D8&shareId=61115562188&businessType=ProductDetail&platform=AE&terminal_id=2ccab959b9674ce68c71c9f0693923f9&afSmartRedirect=y&gatewayAdapt=glo2fraATtiny13.jpg

Il est ainsi facilement démontable pour sa programmation.

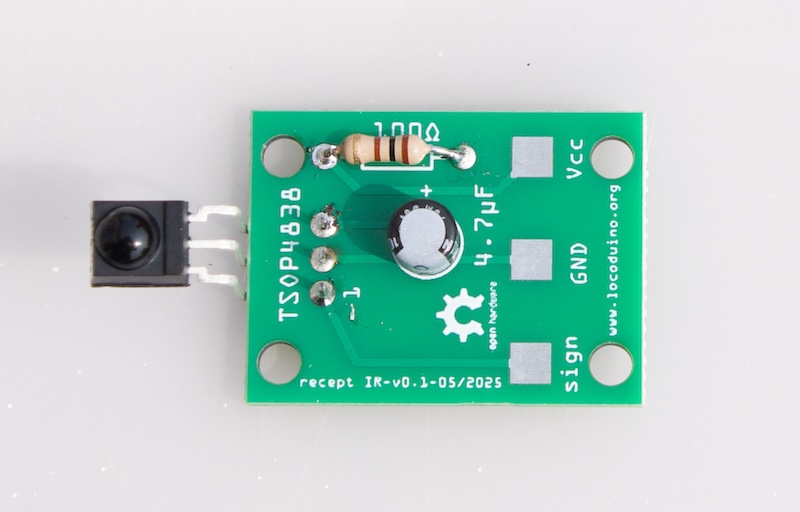

https://www.instructables.com/Updated-Guide-on-How-to-Program-an-Attiny13-or-13a/Pour la commande du servo, il est installé sur un petit circuit imprimé (fabriqué par JLCPCB) qui est relié:

- aux 4 fils émaillés du sémaphore (masse et Vert-Jaune-Rouge) soudés directement sur le circuit en JP2.

- au bornier alimentation (+5V, masse) en X1.

- au bornier Vert-Jaune-Rouge des fils venant de la carte CMRI en X2.

- à la prise du servo JP1.

Le circuit comprend les 3 résistances qui contrôlent l'équilibre de l'intensité d'éclairement des leds.

10k ohms pour la led verte qui éclaire, à courant égal, plus que les autres. 560 ohms pour la jaune et la rouge.

Il y a 2 résistances 10k ohms ajustables pour régler la butée haute et basse de déplacement du servo.

Il y a aussi 2 condensateurs de découplage de l'alimentation.

SemATtinyV2.jpg

SemATtiny_sch.png

SemATtiny_brd.png

Fichiers Gerber (zip) du circuit en pièce jointe

sema reseau.jpg

sema reseau 2.jpg

La programmation se fait à bas niveau car l'ATtiny13 ne possédant qu'un seul timer 8 bits,

il n'est pas possible d'utiliser la librairie Servo (timer 16 bits).

Le programme configure le timer 0 en mode CTC pour fabriquer (avec une fonction d'interruption) un signal PWM (50Hz) de commande de servo.

Il y a 2 programmes en pièces jointes qui font tourner le servo doucement, entre 2 positions de butée, soit en sens horaire soit en sens inverse:

servotiny13_clockwise.ino

servotiny13_counterclockwise.ino

On choisit l'un ou l'autre selon le sens de montage du servo sur son support.

A noter que ce programme peut également servir à commander un servo pour commande d'aiguillage.

Il faut une alimentation 5V suffisante pour alimenter tous ces servos.

J'utilise une alimentation à découpage 5V 10A pour mon réseau qui comprend:

- 5 cartes de détection 4 cantons

- 1 carte contrôle de plaque tournante à base d'arduino Nano

- 1 carte d'entrées / sorties CMRI à base d'arduino Nano

- 12 cartes de commande de sémaphores par servo

https://youtube.com/shorts/DJsfztdC8tI?feature=share .

.